オペアンプの応用

前節までは主にオペアンプの回路トポロジや回路動作など について説明してきましたが この節では実際に オペアンプ どのように使うのかという、アプリケーションの観点で話をしていきます。

仮想短絡という考え方

オペアンプを使う場合には仮想短絡 (Virtual Short)という考えかたをすると便利です。

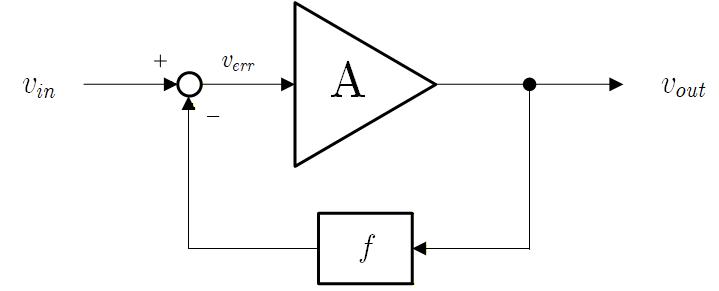

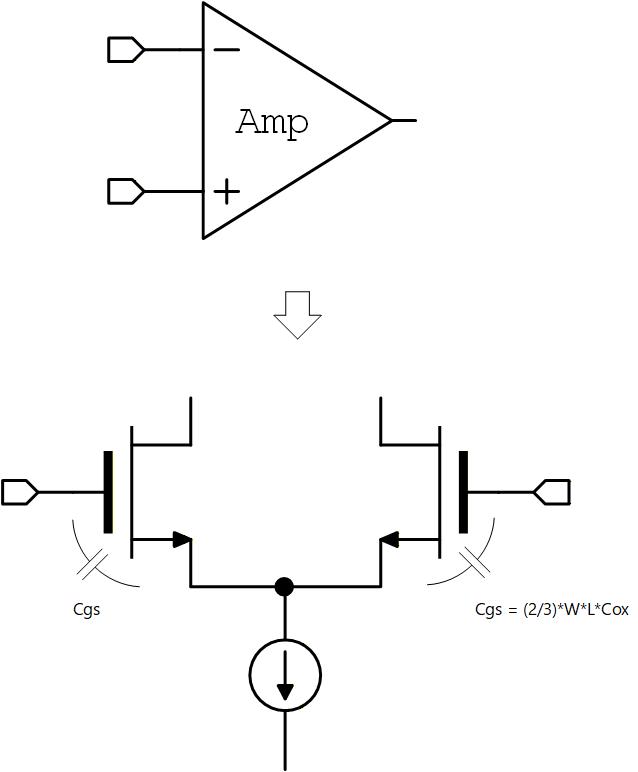

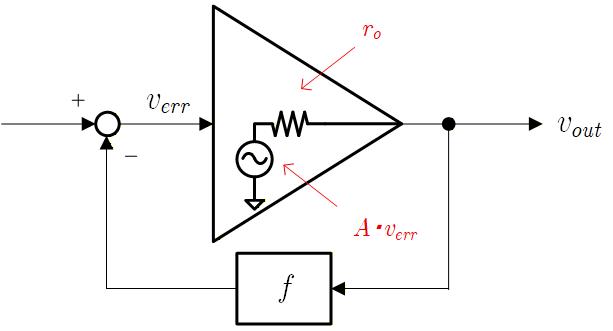

アンプにフィードバックをかけた時のブロック ダイアグラムは Fig. 3-1a のようになります。 入力信号 から を減じた誤差電圧 () をアンプにより 倍された出力が として現れます。 これを式で表すと

となって、 が大きくなるにしたがって誤差電圧は小さくなります。

このブロック線図をオペアンプを用いた回路図に置き換えたものが Fig. 3-1b になり、 はオペアンプの反転入力端子(POS)と非反転入力端子(NEG) の電圧の差に相当します。 したがって が大きくなると POS電圧とNEG電圧の差は小さくなり、 とすれば となります。

つまり が十分大きく、POS 端子とNEG 端子が同電位になって短絡されたように見えます。これを仮想短絡と呼び、オペアンプの場合には POS 電圧とNEG 電圧は同じになるようにフィードバックがかかるともいえます。

仮想短絡の考え方を使うとオペアンプ使った回路の動作を簡単に把握することが可能です。

Fig. 3-1a

Fig. 3-1b

POS端子あるいはNEG端子のどちらかが接地 (グラウンド) になっている場合を仮想接地と言います。

反転増幅

抵抗でフィードバック

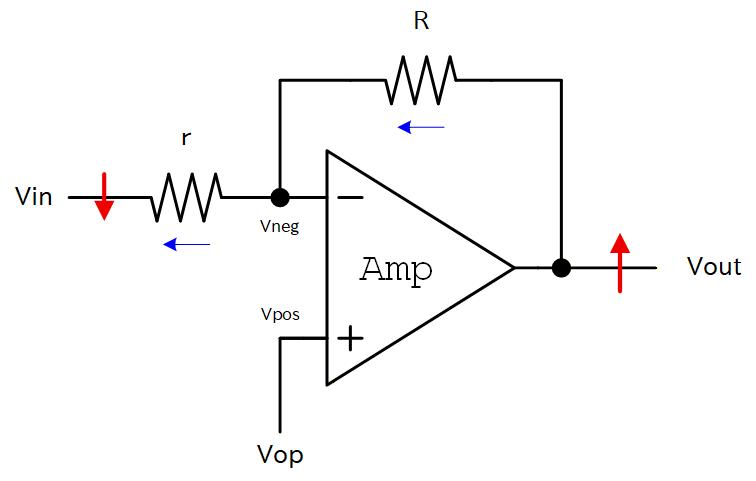

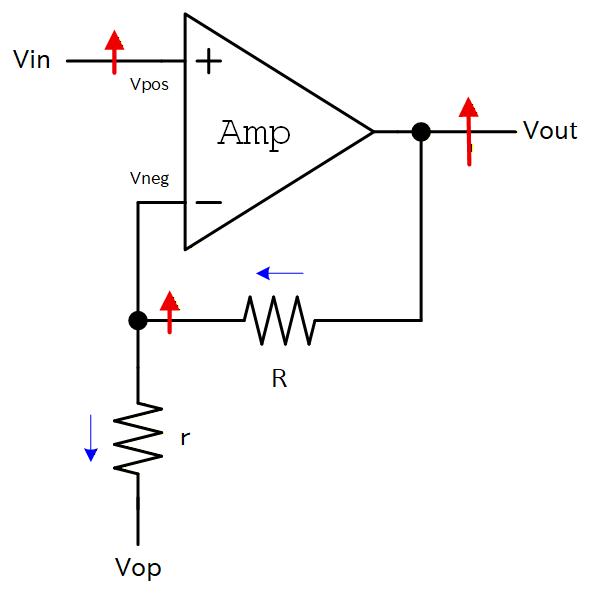

Fig. 3-2a に抵抗を使ってフィードバックをかけた場合の反転増幅回路を示し、入出力の関係を求めてみます。

なお、図で は動作点電圧を意味し、定電圧を与えます。

Virtual Short により となるので

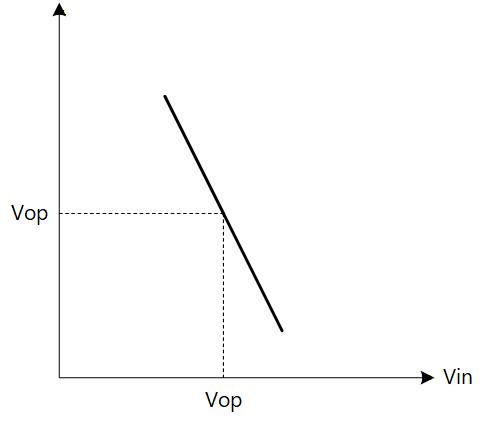

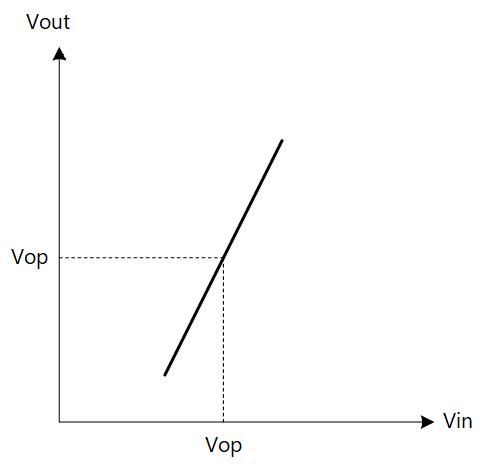

が得られます。Fig. 3-2b に入出力特性のグラフを示しますが、 のときには となり、 を上げると が の増幅率で下がり、 を下げると が の増幅率で上がるように入力を逆相で、すなわち反転増幅することがわかります。

Fig. 3-2a

Fig. 3-2b

容量でフィードバック

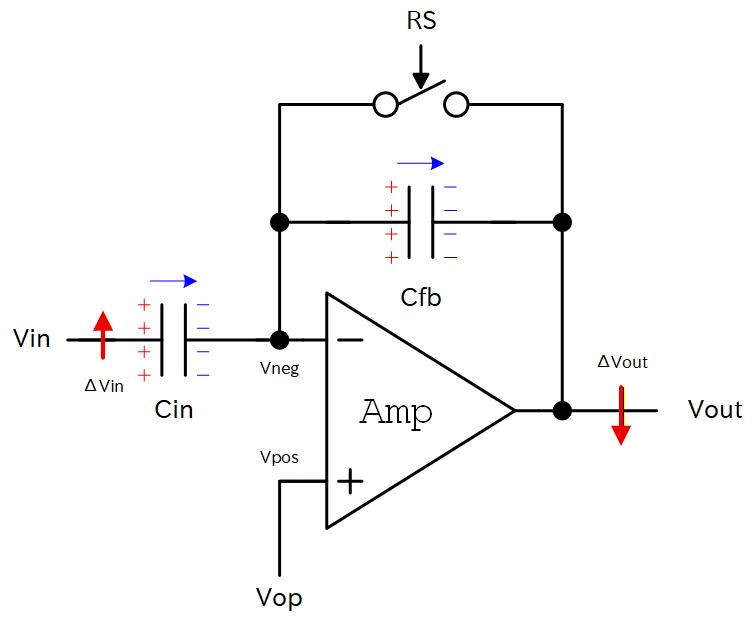

Fig. 3-3a に抵抗ではなく容量を使ってフィードバックをかけた反転増幅回路を示します。

これはスイッチト・キャパシタ回路でよく使われる回路で、入力リーク電流のない CMOS オペアンプの特長を生かした回路になります。

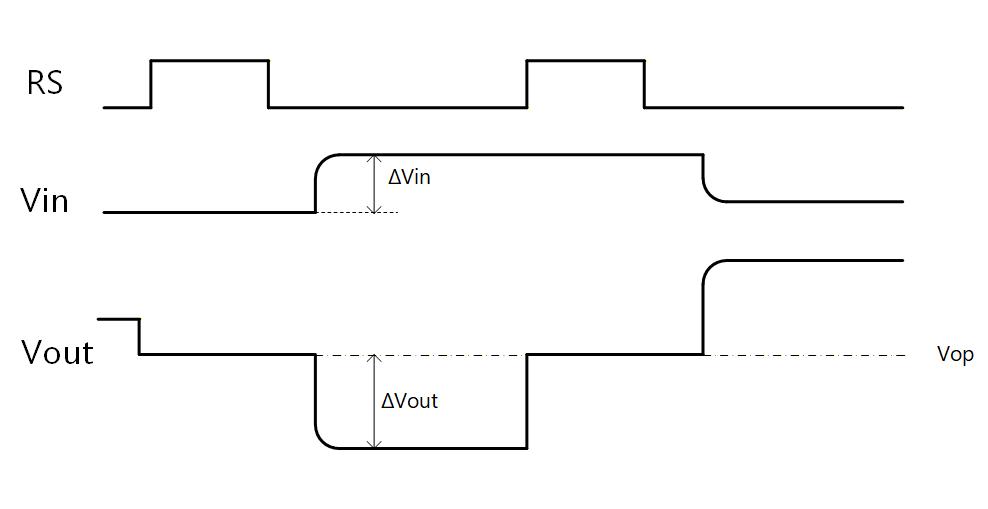

容量は DC でインピーダンスが ∞ になってしまうので、この回路は周期的に OUT と NEG の間を短絡して、動作点をリセットする必要があり、入力信号はリセット前後の電圧差として与えられ、出力信号もリセット前後の電圧差として得られます。

以下、動作を説明します。

リセット中は Voltage Follower を構成するので となり、リセットを解除すると Virtual short によって ノードは 電圧が維持されます。

リセット解除後入力が だけ変化すると電荷の再分配が起こり、出力が だけ変化することになります。

に蓄積される電荷は を使って

に蓄積される電荷は を使って

電荷保存則から

したがって出力は

だけ変化する (Fig. 3-3b) ように振る舞います。

Virtual Short により となるので

が得られます。Fig. 3-3 に入出力特性のグラフを示しますが、 のときには V となり、 を上げると が の増幅率で下がり、 を下げると が の増幅率で上がるように入力を逆相で、すなわち反転増幅することがわかります。

Fig. 3-3a

Fig. 3-3b

非反転増幅

オペアンプの代表的なアプリケーションとして、入力と出力が同相で変化する非反転増幅回路があります。(Fig. 3-4a)

以下、動作を説明します。

Virtual Short により となるので

が得られます。Fig. 3-4b に入出力特性のグラフを示しますが、 のときには となり、 を上げると が の増幅率で上がり、 を下げると が の増幅率で下がるように入力を同相で、すなわち非反転増幅することがわかります。

Fig. 3-3 に入出力特性のグラフを示しますが、 のときには となり、 を上げると が の増幅率で下がり、 を下げると が の増幅率で上がるように入力を逆相で、すなわち反転増幅することがわかります。

Fig. 3-4a

Fig. 3-4b

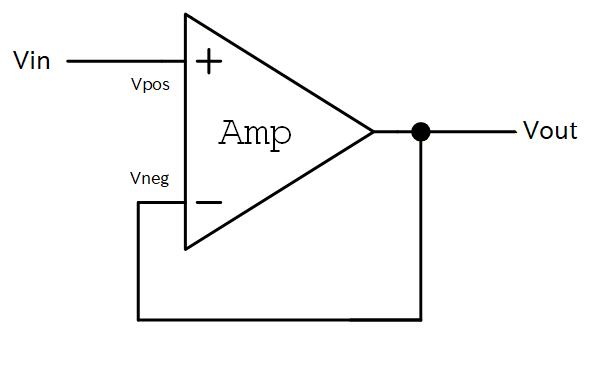

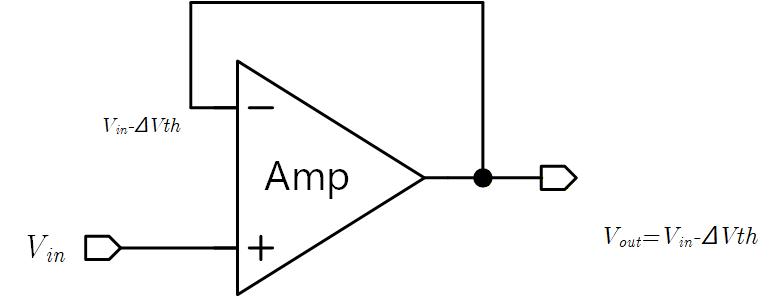

Fig. 3-5 に示す回路は、上記の非反転増幅回路で , とした場合に相当します。

Virtual Short により だから

となり、入力された電圧をそのまま出力する Voltage Followe 回路となることがわかります。

増幅はしませんが、インピーダンスが高い信号のインピーダンスを下げる、いわゆるインピーダンス変換回路として使われます。

Fig. 3-5

「アナログ回路の基本要素」 で、インピーダンス変換回路として Source Follwer について説明しましたが、Source Follower は入力と出力のレベルがずれるとか、ゲインが 0dB を下回という欠点があります。 それを嫌う場合に Voltage Vollower を使います。

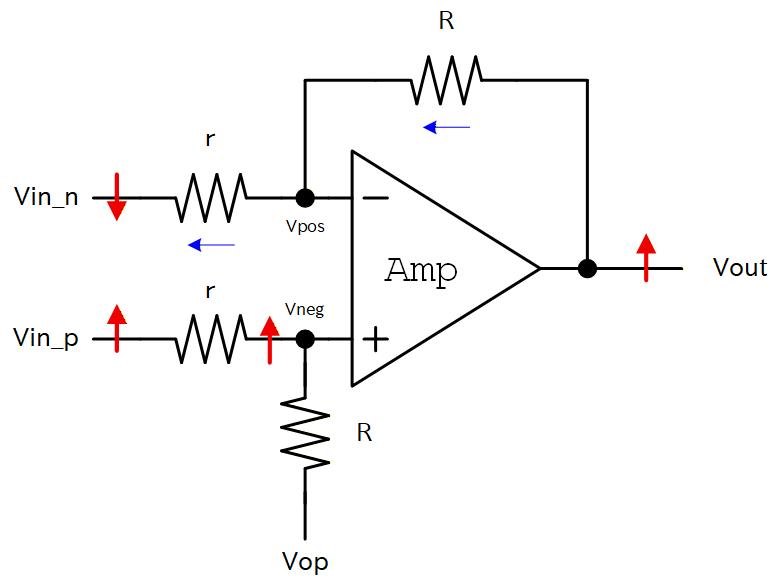

差動増幅

オペアンプの代表的なアプリケーションとして、POS 入力と NEG 入力の差分を増幅する、差動増幅回路があります。(Fig. 3-6a)

以下、動作を説明します。

Virtual Short により となるので

が得られます。Fig. 3-6b に入出力特性のグラフを示しますが、 として、 のときには が の増幅率で上がり、 を下げると が の増幅率で下がるように と の差電圧を増幅することがわかります。

Fig. 3-6a

Fig. 3-6b

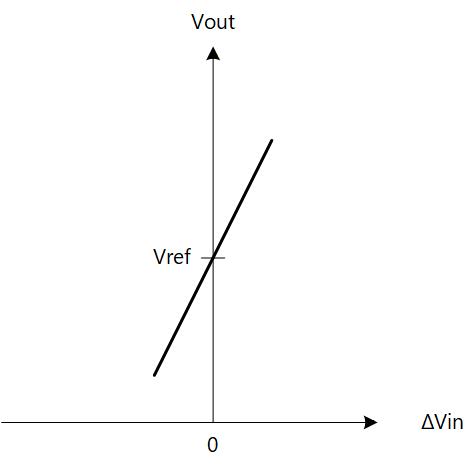

電流-電圧 変換回路

オペアンプのちょっと変わったアプリケーションとして、入力された電流を電圧に変換して出力する回路があります。

これは電流を出力するようなセンサー、例えばフォトダイオードを使う場合に扱いやすい電流に変換するなどの目的で使われます。(Fig. 3-7)

入力される電流を とすると、CMOS アンプの入力抵抗はほぼ ∞なので電流は全てフィードバック抵抗に流れ、電位降下を引き起こします。

POS 端子には動作点電圧 を与えると、Virtual Short により も になるため、

これにより の場合には で、信号電流 が発生するとフィードバック抵抗 で決まる変換インピーダンスで信号電圧 に変換されることがわかります。

Fig. 3-7

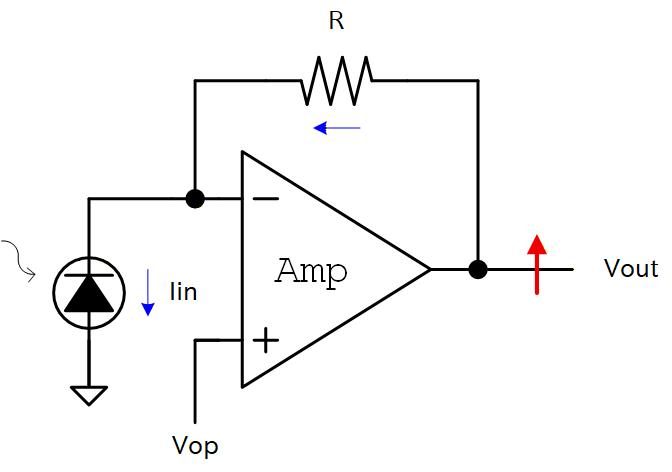

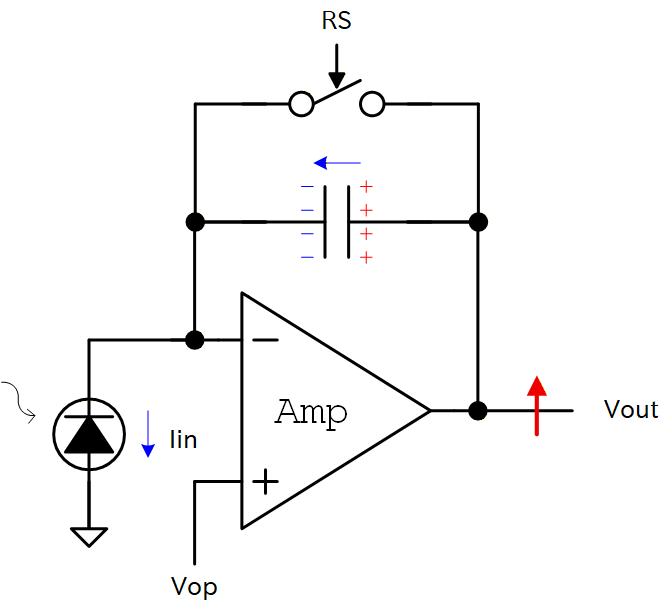

電流積分回路

前節で電流を電圧に変換する回路を紹介しましたが、微弱な光を検出する場合はフォトダイオードで電変換された微弱の電流をそのまま抵抗で電圧に変換するのではなく、積分して扱いたい場合などに使います。そのような場合は Fig. 3-8a のような電流積分回路を使います。

これは、先に解説した「容量を使った反転増幅回路」と同様に容量は DC でインピーダンスが∞になってしまうので、周期的に OUT の NEG の間を短絡して、動作点をリセットします。

リセット中は Voltage Follower を構成するので となります。

リセットが解除時には Vvirtual short によって ノードは 電圧が維持され、その後信号電流は容量に流れ込みます。 信号電流を Iin とし、リセット後の経過時間を T とするとフィードバック容量に蓄積される電荷は

これがフィードバック容量で電圧に変換されるため

と、経過時間とともに信号電流が積分されていく波形が得られます。(Fig. 3-8b)

Fig. 3-8a

Fig. 3-8b

上記の例では光によって電流が変化する素子と定容量を使って光の強さを求めましたが、ある物理量によって容量が変化するような素子があったときには、逆に定電流を流して電圧変化を検出すれば、その物理量の変化を求めることが可能です。

オペアンプの特性項目

これまでオペアンプの内部回路の話とアプリケーションの話をしてきましたが、オペアンプを使う上で重要な特性項目と、それが内部回路のどこに起因するかについて整理します。

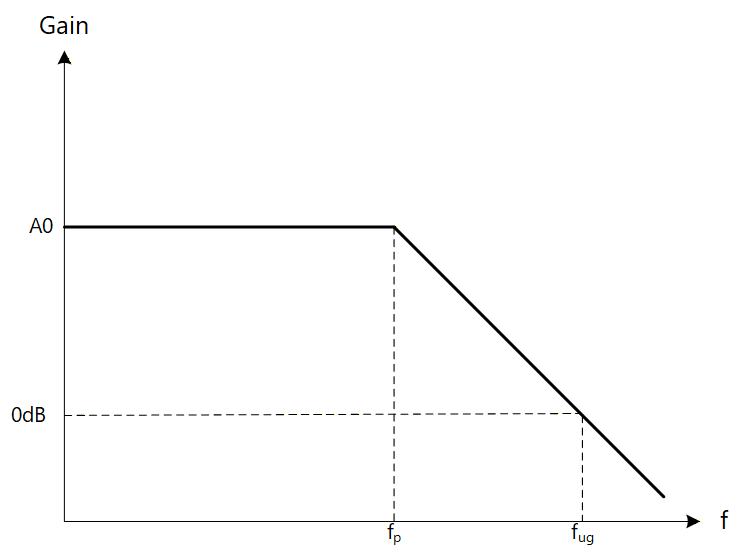

オープンループゲインと帯域幅

オープンループゲインはフィードバックをかけない状態での DC (f=0) でのゲインを指しますが、これはトランジスタの と および 段数で決まります。

, はトランジスタのディメンション・バイアス電流・与える 以外に、そのプロセスのパフォーマンスにも依存します。

段数については多段にすることでゲインを稼ぐことは可能ですが、一般にゲインを高くすると位相補償が難しくなってきますので注意が必要です。

帯域幅は GB積で表され、オープンループゲインとドミナントポールの周波数の積として定義され、多くの場合はオープンループゲインが 0dB を割り込む、Unity Gain 周波数と同じになります。

一般的にオープンループゲインとドミナントポール周波数はトレードオフの関係にあるため、1つのオペアンプだけで高帯域・高ゲインの増幅を行うことは困難です。

このためシステムとして実現するときには高帯域で低いゲインのフィードバックアンプを何段か積み上げて所望のゲインを得るような工夫が必要となります。

Fig. 4-1

入力オフセット

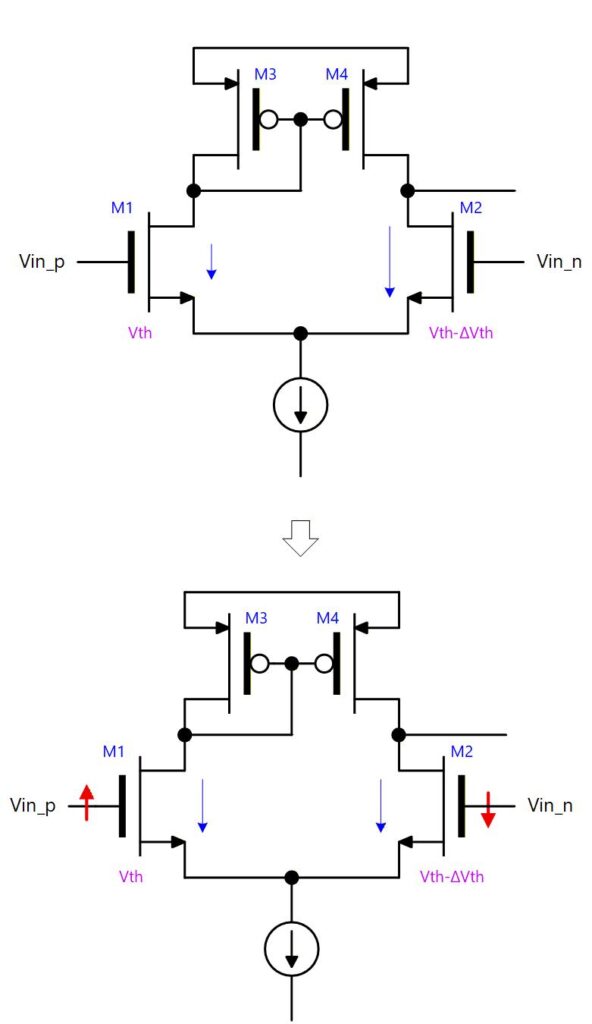

これまでは言及してきていませんでしたが、同じチップ上で近接位置にある2つのトランジスタであっても、その特性が全く一致することはありません。

特に問題になるのは のミスマッチで、これがいわゆる入力オフセットの原因となります。

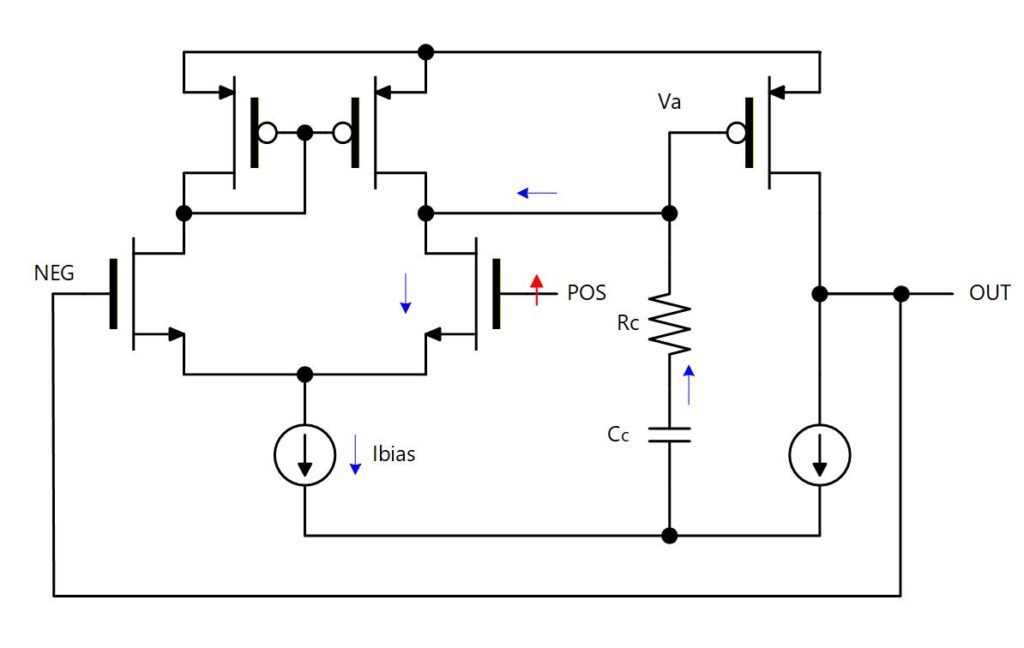

Fig. 4-2 にオペアンプでよく使われるシングルエンド出力の差動対の回路図を示します。

理想的には M1 と M2 を流れる電流は等しくなりますが、例えば M2 の方が だけしきい値電圧が M1 より低かった場合には

M2 に流れる電流が M1 よりも増えます。

オペアンプにフィードバックをかけて使うと、この電流が等しくなるように の電圧が の電圧より下がった状態でバランスするように作用します。

これが入力オフセットで、このアンプで例えば Fig. 4-3 のような Voltage Followe を構成すると、本来 と等しい電圧が に出力されるべきところが、 だけズレてしまうことになります。

特に微小電圧を扱う場合には大きな問題となります。

なお、ここでは話を単純にするため入力トランジスタの 差のみに着目しましたが、実際にはすべての素子のミスマッチの影響を入力トランジスタの に帰着させたものが入力オフセットとなります。

Fig. 4-2

Fig. 4-3

しきい値電圧のミスマッチの原因やそれを抑える方法などについては、Appedix-2 で解説します。

入力インピーダンス

一般的にオペアンプでは入力のインピーダンスを考慮する必要があります。

バイポーラトランジスタの場合にはゲートに相当するのがベースで、そこには DC 電流が流れますが、MOS トランジスタの場合にはゲートは絶縁膜(Oxide) で分離されているのでいわゆるリーク電流はほとんどなく、入力抵抗は ∞です。

ただし、MOS トランジスタの場合にはゲート容量が存在するため、入力容量は無視できません。

特にトランジスタサイズを大きくしたオペアンプを、高い出力抵抗の前段で駆動するときには、そこて発生する CR 時定数によって帯域を損ねる場合があるので注意が必要です。

Fig. 4-4

出力インピーダンス

「フィードバック」 の章でも解説しましたが、出力端子から見える抵抗をループゲインで割ったのがオペアンプの出力インピーダンスになります。(Fig. 4-5)

2段増幅型のアンプの場合の出力抵抗は で決まるのでそれをループゲイン

( ) で割ると

と、大幅に下がりますが、Cascode 型アンプの場合は出力抵抗が と非常に大きくなっているので、ループゲインで割ると

と、それほど下がらないことに注意が必要です。

Fig. 4-5

入出力電圧範囲

オペアンプの入出力電圧範囲は広ければ広いほど汎用性が高まり有利ですが、「オペアンプ(前編)」の Fig. 2-3 や Fig. 1-3 に示したように制限があります。

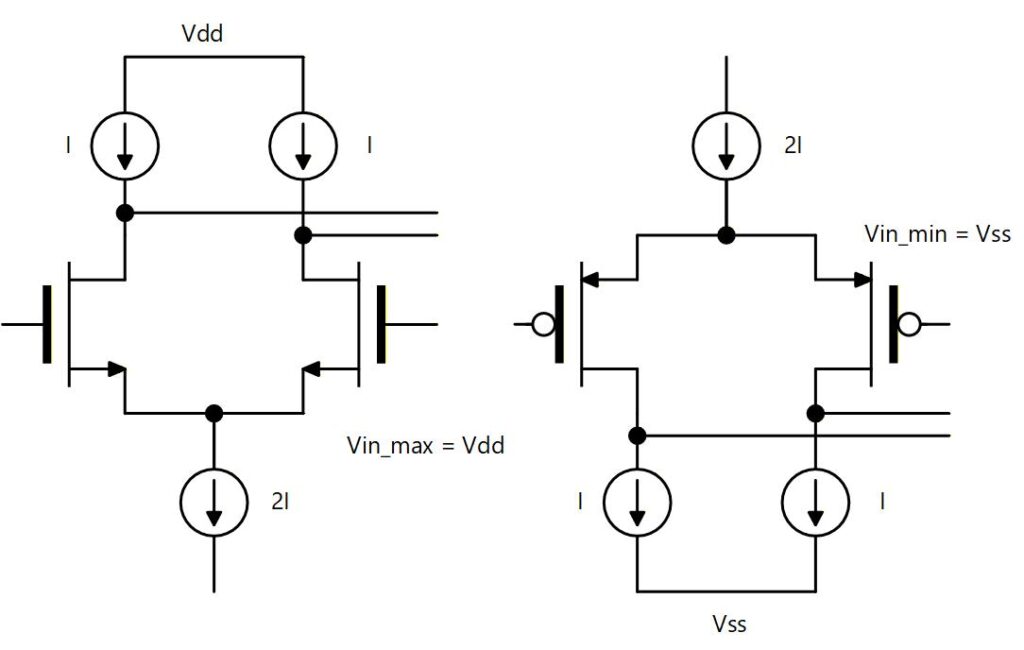

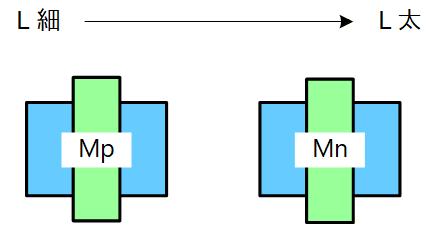

Fig. 4-6 左図 のような NMOS 入力の差動対を用いた Cascode 型オペアンプの場合には、Fig. 2-3 に示したように入力可能な電圧は電源電圧まで上げることが可能です。

同じように Fig. 4-6 右図のような PMOS 入力の差動対の場合に入力可能な電圧はグラウンドまで下げることが可能です。

したがって、この 2つを組み合わせると入力電圧範囲として、グラウンドから電源電圧までの全範囲をカバーできるオペアンプが可能です。

Fig. 4-6

電源電圧やグラウンドを Rail と表現することがあります。 NMOS 入力の差動対と PMOS 入力の差動対を組み合わせると、入力範囲を電源電圧からグラウンドまで取ることができ、これを Rail-to-Rail と呼びます。

出力に関しては残念ながら 制約があるため、Rail-to-Rail 出力は困難です。

電流駆動能力

容量性負荷の駆動

オペアンプの負荷として大きな容量がつくと、出力インピーダンスと負荷容量で形成される Pole が低周波に動きます。

2段増幅型のオペアンプのように、それが 2nd Pole だった場合には 1st Pole との周波数差が小さくなるので位相余裕に注意が必要になります。

Cascode 型のように、それが 1st (Dominant) Pole であれば位相余裕の問題はありませんが、帯域(GB積) が悪化することになります。

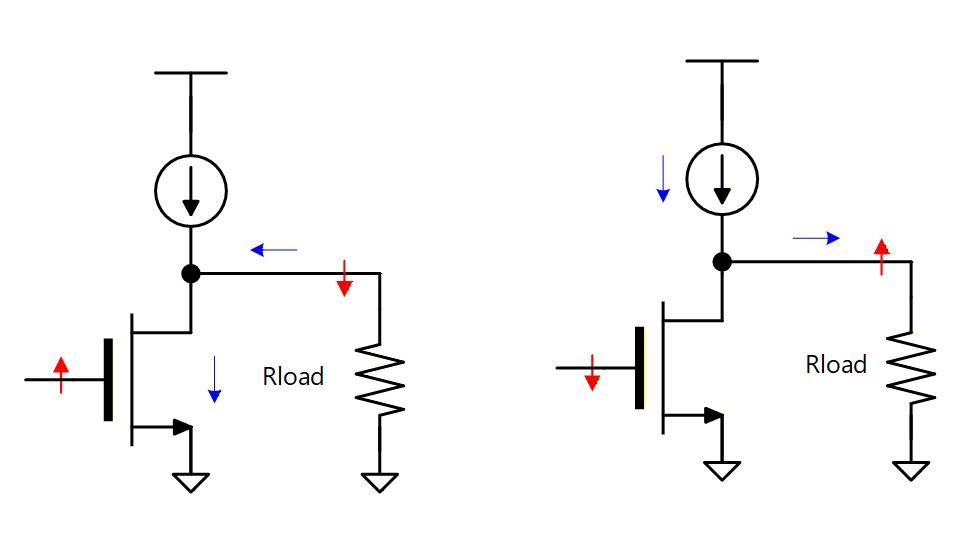

抵抗性負荷の駆動

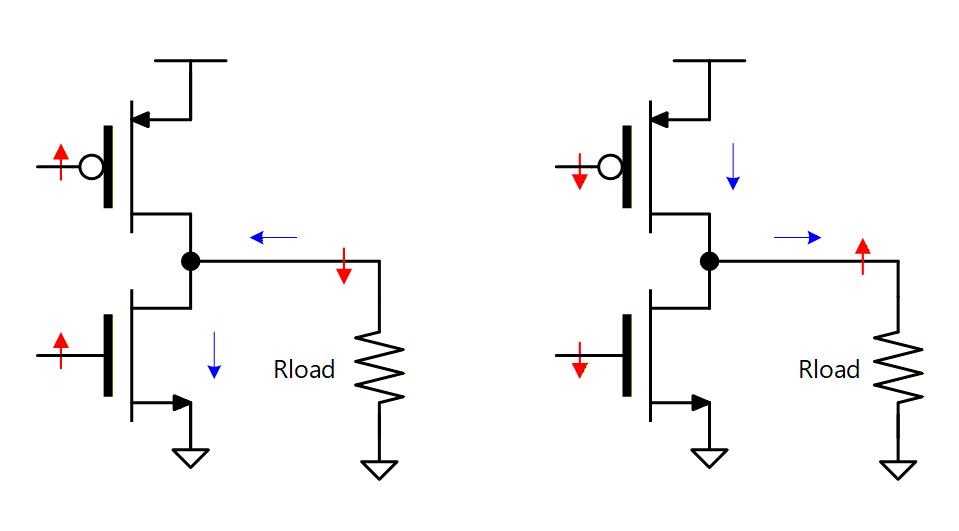

低抵抗負荷を駆動するには大きな出力電流が必要になります。電流源を使ったインバータを用いると、Fig. 4-7 左 のように出力を下げるときにはトランジスタで駆動するので大電流を流すことは可能ですが、Fig. 4-7 右のように出力を上げるときには電流源で駆動するので、限界があります。

電流源の電流を大きく取れば、低抵抗負荷でも駆動できるようになりますが消費電流が増えるので好ましくはありません。

Fig. 4-7

低抵抗負荷を駆動する必要がある場合は、Fig. 4-8 に示すような、Push/Pull 型のインバータを使うのが望ましいです。

出力を下げるときは Pull 側の NMOS トランジスタで駆動し、出力を上げるときには Push 側の PMOS トランジスタを使うことで、どちらの場合も大電流を流すことができます。

ただし、Push/Pull 型を使う場合には、Push 側、Pull 側ともに最適な を与えることがポイントで、工夫が必要です。

Fig. 4-8

スリューレート

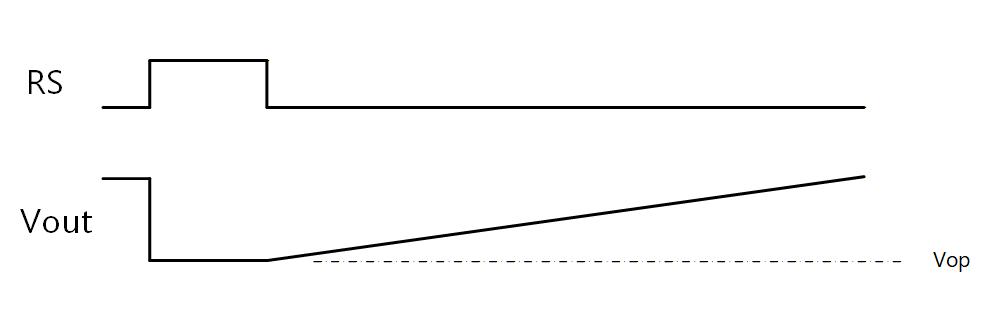

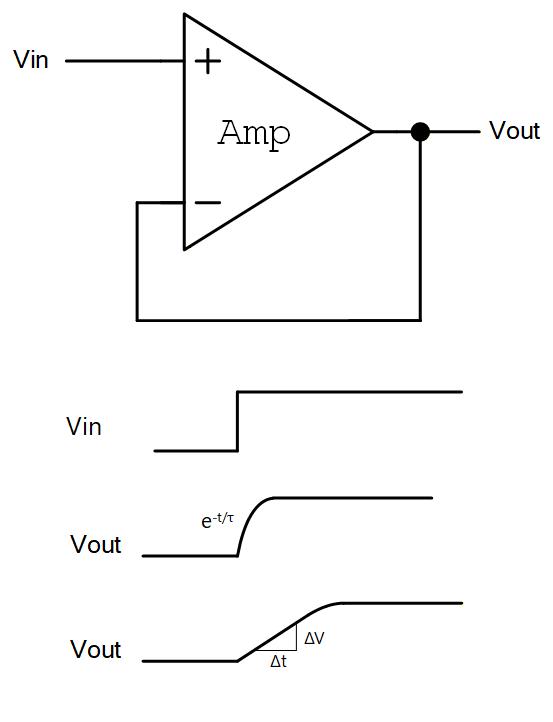

Fig. 4-9 に示すように、Voltage Follower にステップ入力を与えた場合を考えます。 として期待されるのは、時定数 で立ち上がる 2番目の波形ですが、実際には のレートで立ち上がる 3番目の波形になることがほとんどです。 この をスリューレートとよび、オペアンプの特性項目のひとつです。

小信号特性はあくまでも各素子に流れているバイアス電流がほとんど変化しない場合の特性ですが、ステップ入力で、その振幅が大きい場合には素子を流れる電流は大きく変化し、ときに電流が枯れたりする場合もあり、 “小信号特性” と “大信号特性” は区別する必要があります。

実は、大信号のステップ入力が POS ノードに印加されると、OUT ノードの電位を上げて Virtual Short を保持しようとしますが、 ノードの電位は位相補償容量が接続されているため、直ぐには下がりません。

電圧が所定の電圧 ( とするのに必要な電圧) に達するまでは、差動対の電流 で位相補償容量 を放電する必要があるため は で決まるレートで直線的に変化していくことになります。

したがって、 が小さい場合や が大きい場合には整定電圧に至るまで時間がかかることになります。

Fig. 4-9

Fig. 4-10

まとめ

これまでオペアンプ内部の回路構成や動作、並びに具体的な使い方、また使う上での特性と内部の回路との関連などについて解説してきましたので、オペアンプ全般についての理解が深まったと思います。

これらの知識を活用すれば、今回紹介したオペアンプにとどまらず、数多のオペアンプから用途や目的に合わせて最適なものを選定したり、それを自在にカスタマイズすることもできると思います。

とりあえずアナログ回路の設計講座としては今回のオペアンプの章で一旦終了しますが、一連の講座を通してオペアンプを含む各種のアナログ回路の設計に必要な基礎知識は網羅できたのではないかと考えます。

閲覧ありがとうございました。

Appendix-2 トランジスタの理想と現実

集積回路の設計においては、回路図をレイアウト図に、レイアウト図をフォトマスクに、フォトマスクから物理的な半導体素子へと変換され、それらの素子同士が同じくレイアウト図・フォトマスクを介して形成されたメタル配線で接続されることで、シリコン上に実回路を形成します。

回路図においては同じディメンションで指定された素子はすべて同じ特性を示しますが、シリコン上の実回路には回路図には見えない様々な誤差要因が入り込みます。

ここでは特にトランジスタについて、回路図と実回路、すなわち理想との現実のギャップについて簡単に解説します。

回路図上では配線は抵抗ゼロ・容量ゼロですが、集積回路上では有限の抵抗・有限の容量を持ちますので、回路の特性に影響を及ぼします。 この配線抵抗や容量はレイアウトする前の回路設計段階では確定していないため、レイアウト前の設計検証を Pre Layout Simulation (略して Pre Sim) と呼び、レイアウト後に確定した抵抗や容量を組み込んで行う設計検証を Post Layout Simulation (略して Post Sim) と呼びます。

ロケーションによる特性の差異

トランジスタに流れる電流は以下の近似式で表されます。(5極管条件)

, , , が同一のトランジスタであれば、同一の をかければ流れる電流は同じですが、実際には誤差を生じます。

トランジスタの , はエッチング工程で決定されますが、エッチングレートが完全には均一にならないため、ウェハ内はもとより、チップ内でも場所によっても W や L に差異が発生します。

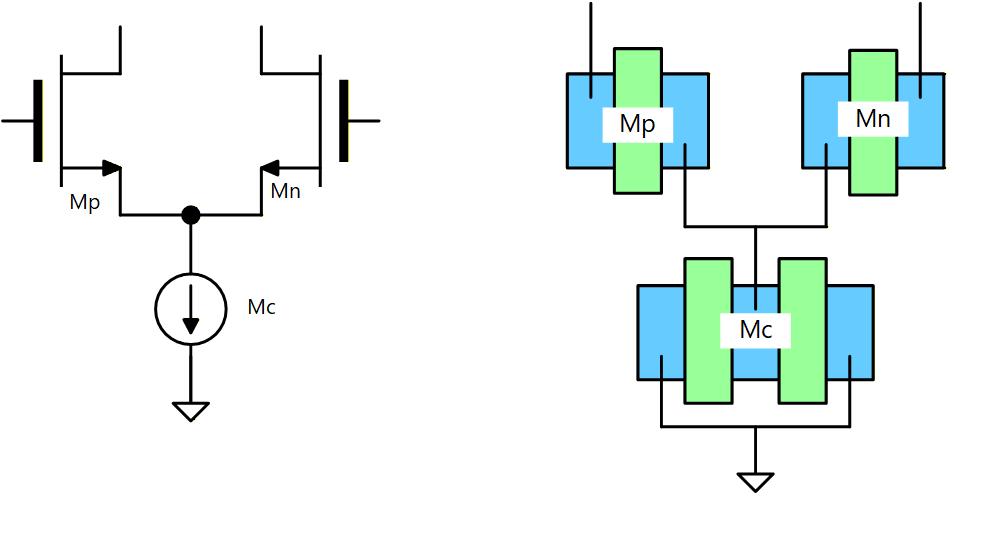

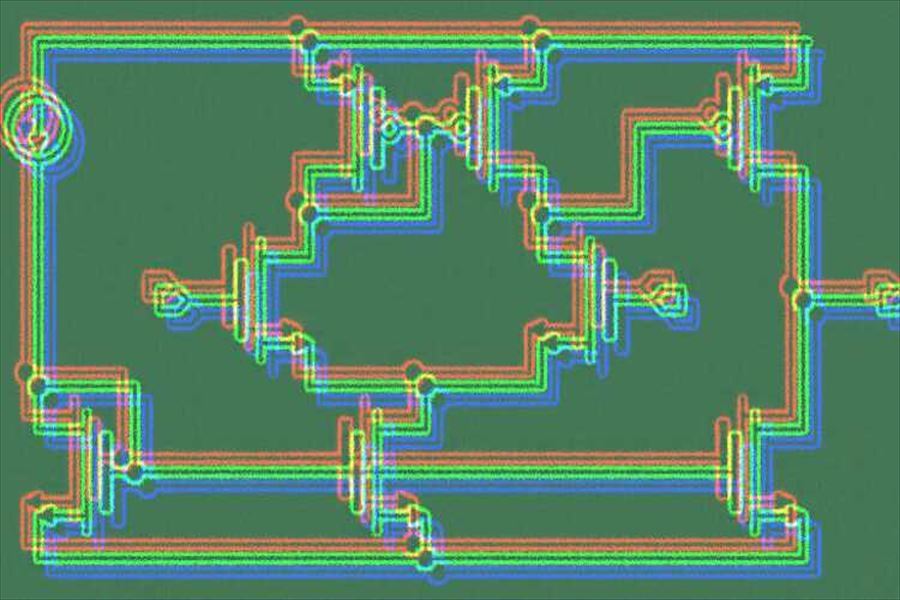

Fig. A2-1 に例として差動対の回路図とレイアウト図を示しますが、Fig. A2-2 のように場所によって L が異なると、同じ入力電圧を与えても流れる電流が異なり、入力オフセットが発生します。

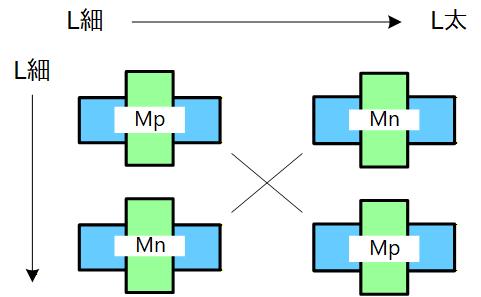

このように2つのトランジスタの特性をなるべく等しくしたい場合にはFig. A2-3 に示すような Common Centroid レイアウトを行います。

Centroid とは “重心” という意味で、2つのトランジスタの重心が共有になるようにレイアウトする手法です。

ここでは x方向、y方向ともに傾斜がある場合を示していますが、両方向について平均をとることになるため、不均一性が緩和されて入力オフセットが低減できます。

以上、エッチングの不均一性が特性差に影響を及ぼす例を示しましたが、これ以外にも STI (Shallow Trench Isolation) による素子分離を行う場合には STI から近いトランジスタは応力により移動度が下がるという、STI ストレスなどによっても特性差を引き起こします。

Fig. A2-1

Fig. A2-2

Fig. A2-3

バラツキによるランダムな特性の差異

上記のエッチングの不均一性などに起因するトランジスタ間の特性差以外にも、素子バラツキに起因するランダムな特性差があります。

これは例えばトランジスタの がゆらぎを持つためにランダムにバラツくような現象で、微細なトランジスタになるほど顕著になります。 を所定の値にするためにイオン注入によるしきい値調整を行うのが一般的ですが、注入されるイオンの密度が均一にならないために起こります。

これは統計的に不可避で、ランダムな事象であるためレイアウトを工夫するなどの方法では解決しません。

改善するための唯一の方法はトランジスタのサイズを大きくすることです。

通常、これらのバラツキはトランジスタの面積に依存し、面積を 2倍にするとバラツキは 1/√2 になります。

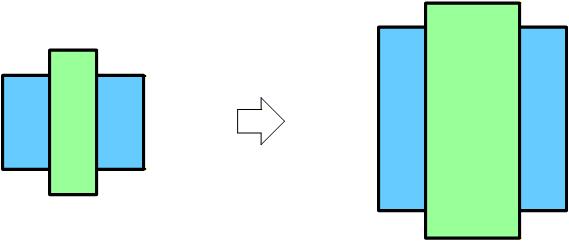

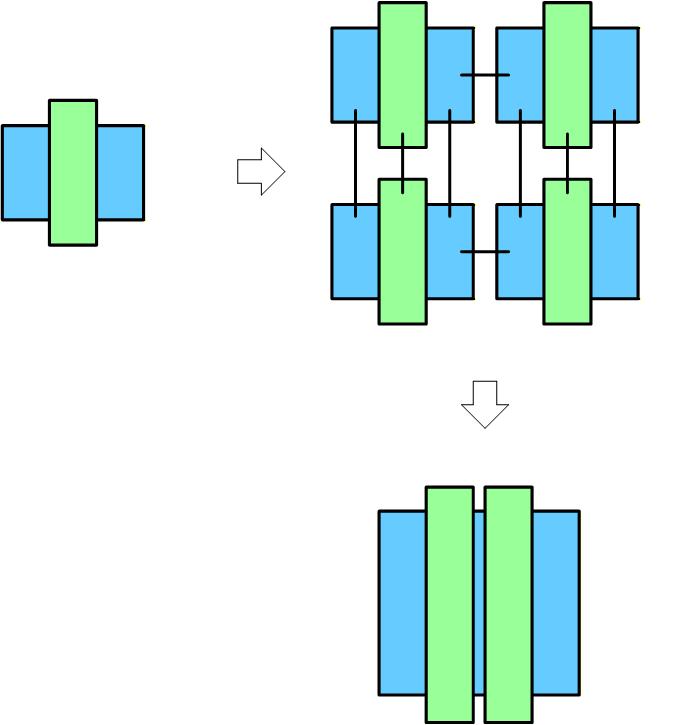

だけ、あるいは だけを大きくすると流れる電流も変わるので、Fig. A2-4a のように 比を維持したまま と を連動して面積を大きくするか、Fig. A2-4b のようにトランジスタを縦・横に並べて相互接続して実効的な面積を大きくするなどの手法を取ります。

Fig. A2-4a

Fig. A2-4b

まとめ

オペアンプなどのように、トランジスタの特性が直接回路の特性に影響するようなアナログ回路の場合には、回路図レベルの設計の段階から、シリコン上で出来上がるトランジスタの誤差要因を意識して、対策を考えていく必要があります。

それがアナログ回路の難しい点ですが、面白い点でもあると思います。

コメント